�������: 1-15 ���鵽�����ӿ�ѧ�뼼�� ����������ؼ�¼18�� . ��ѯʱ��(0.16 ��)

�й���ѧԺ���㼼���о����Ⱥ����о�Ա���ƹ����о�Ա������о��Ŷ����й���ѧԺ�Ϻ�ϵͳ����Ϣ�����о��������¼�ơ��Ϻ�ϵͳ�������ν��о�Ա�Ŷ����Ϲ��أ������˳�������̬������ԭ��оƬ��������SUSHI����������һ����ڳ�������ͨ���ӣ�SFQ����·�ij�������оƬ����оƬ�����Ϻ�ϵͳ���������ɵ�·���ƽ̨չ����ƣ������Ϻ�ϵͳ�������з���SIMIT Nb03�������ɵ�·���գ��䱸PDK����Ԫ��...

�й���ѧԺ���㼼���о����о�Ա�Ⱥ������ƹ���������о��Ŷӣ������˳�������̬������ԭ��оƬ����������SUSHI��������������һ����ڳ�������ͨ���ӣ�SFQ����·�ij�������оƬ������SFQ��·ͬʱ���г������ٶȺͳ��ͼ��㹦�ĵ��ص㣬����ͻ�ƴ�ͳ�����ڵ�λ����͵�λ�ܺ������������������ѵ�ƿ����2023��������������оƬ��Ϊ��ԭ������������о��ȵ�֮һ��

���пƼ���ѧ��ѧ�������ϢѧԺ������ʦ�������ڻ���ת�ô洢����֧��Ƭ��ѧϰ�Ķ���칹 �˹������������о�����ȡ�ý�չ��ͼ��

���пƼ���ѧ��ѧ�������ϢѧԺ ���� ת�ô洢�� ����칹 �˹����� ������

2021/11/8

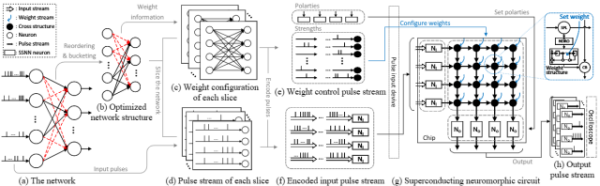

��������������磨DNN��Ϊ������AIģ�͵ķ��ٷ�չ����������ʶ�������������ճ�Ӧ���б��㷺Ӧ�á�Ȼ���ڹ������ı�Ե���㣨Edge Computing�������������� ��AIoT�������У��߹��ĵĴ�ͳ���ѧϰƽ̨���Է���������ܵ����ơ���������������ѧ����Ը���ЧӲ���������о��Ĺ㷺��ע��ּ�ڼ���AIoT�ն�Ƭ��ѧϰ��������Ҫ���ܺġ�����������磨Deep Belief Network, DB...

������ѧ�����������ϢѧԺ���Ӽ����μ������� ������������

������ѧ �����������ϢѧԺ ���Ӽ��� �μ� ������ �����Դ�����

2020/4/13

������ѧ�����������ϢѧԺ���Ӽ����μ������� ��������������

������ѧ�����������ϢѧԺ���Ӽ����μ������� ����������

������ѧ �����������ϢѧԺ ���Ӽ��� �μ� ������ ���Դ�����

2020/4/13

������ѧ�����������ϢѧԺ���Ӽ����μ������� ������������

�й���ѧԺ�뵼���о���������о����Wi-Fi����������IP����

�й���ѧԺ�뵼���о��� ��о���� Wi-Fi���������� IP����

2011/12/15

2011��12��13�գ��й���ѧԺ�뵼���о��������пư뵼�弯�ɼ����з���������˾����о���ɣ�SmartChip Integration-SCI��������Wi-Fi������Baseband�������������ѱ�ȫ��ͨ�������쵼������IP�ںϷ�ʽ���ò���֮��Ӧ����ƽ̨�������ϡ���о������ӵ������֪ʶ��Ȩ��Wi-Fi������ó���չ��������Ϊ���Ʒ���ṩȫ���Wi-Fi���ߴ����������������ó��̲�Ʒ�����ͽ���...

ARMΪ�����ֻ��������»�ͼ������

�����ֻ� ��ͼ ������

2011/11/30

ARM�Ƴ�Mali-T658��ͼ����������רΪ�����ֻ���superphone����ƽ��װ�����ǻ��͵��ӵȸ�����װ������Ƶ�Midgard�ܹ���ͼ������ϵ���е����²�Ʒ��ARM MPD�����ܼ�IanSmythe��ʾ�������Ŀǰ��Ϊ���������Ե��Ӳ�Ʒ�����õ�Mali-400����Ļ�ͼ������Mali-T658�Ļ�ͼЧ����߿ɴ�10����Mali-T658�Ļ�ͼ����������Ч�ܣ�Ҳ��Mali-T604��ͼ������...

AMD����7��Ƕ��ʽ�������״�֧��DDR3�ڴ�

AMD Ƕ��ʽ ֧�� DDR3�ڴ�

2010/5/5

AMD����Ƕ��ʽϵͳ�������Ƴ�Ƕ��ʽ�汾��PCоƬ�顢ͼ��оƬ�Լ�7��x86�����������а���AMD�ĵ�һ��֧��DDR3�ڴ��HyperTransport3������·��Ƕ��ʽоƬ��

��������������п��ٴ洢��Դ��������ȱ���洢������������Լʵ�ֿ��١�����GPRS����Э�飨GPRS tunneling protocol, GTP�������������⡣����˻��ڲ�¡������(Bloom filter, BF)�����������˵��ʶ��data tunnel endpoint ��identifier�� Bloom filter, DTEID BF���������÷�������ͻ����ת��Ϊ���������⣬ͨ...

�ⷨ�뵼�壨ST���Ƴ�ȫ��Cartesio+���������������غͱ�Я����ϵͳ���ܼ��û�����

Cartesio+������ ���� ��Я����ϵͳ

2009/8/4

ȫ�����ȵij���������Ϣϵͳ�뵼�������̡��������Ӳ�ҵ����뵼�幩Ӧ��֮һ*���ⷨ�뵼�壨ŦԼ֤ȯ���������룺STM���Ƴ�ȫ��Ӧ��������Cartesio+������GPSоƬ����������һ�����غͱ�Я����ϵͳ�����������������ܺ;�ȷ�Ķ�λ���ܣ��Լ��ḻ�ļ�������ӿڣ��ⷨ�뵼���Cartesio+��ʵ�ֳɱ��Ϳռ��Ч�ĵ�������Ϣ����Ӧ�ã����û��������ɫ��

����������Ľṹ����о�

��˴����� ILP TLP

2009/5/5

Χ����ν��ж���������Ľṹ��ƣ����������������һ���⣬��ϴ�ͳ�����������ԭ���Զ���������ṹ��ƽ������о������Ե�ǰ��Ҫ��ҵ����������������о�����ʾ���䷢չ���ƣ�̽����δ�������������Ƶķ�չ����

32λǶ��ʽ������THUMP

������ оƬ 32λǶ��ʽ������ ���ɵ�·

2009/3/5

32λǶ��ʽ������оƬ-THUMP���ڡ�985����Ŀ��������Ƕ��ʽ����CPU�з�����ʮ�塰863�������ģ���ɵ�·�ش�ר���ص���Ŀ��32λ������Ƕ��ʽCPU������֧������ɵijɹ�������THUMPǶ��ʽ����������ҪĿ�����о�����һ�ָ����ܡ����ĵ�Ƕ��ʽ�������Լ���֮����ϵͳ������Ӧ�ó�������������Ŀ�������(1)���Ƴ�һ�־�������֪ʶ��Ȩ��32λǶ��ʽ������оƬ����оƬ������Ƕ��ʽ...

�й���ѧԺ�����о��������һ��������GPS���ǵ��������������㷨��ԭ�ͻ�������ͼ��

������ ���ǵ��� �������㷨 ԭ�ͻ� ����

2009/2/27

�й���ѧԺ�����о���ͨ�����ý��SOC�о��ң����ң�������һ��Ŀ̿�أ�Ŀǰ�ѳɹ������һ��������GPS���ǵ���������������ԭ�Ϳ������������ָ��ﵽ�����Ƚ�ˮƽ��

�ȽϺͷ�����LEON2��OpenRISC1200��NiosII ��3 �ֿ�����RISC ������IP �˵Ľṹ�ص㣬 Ȼ���������������Ϊ������FPGA ƽ̨�Ϲ�����һ������ϵͳ�� ����Dhrystone 2.1 �����Գ������������ǵ����������0.18um ��CMOS�����½������ۺϣ� ������������ASIC ƽ̨�������Ƶ�ʵıȽϡ�

�й��о����������а�-��

- ���ڼ���...

�й�ѧ���ڿ����а�-��

- ���ڼ���...

�����ѧ���л������а�-��

- ���ڼ���...

�й���ѧ���а�-��

- ���ڼ���...

�ˡ���-ƪ

- ���ڼ���...

�Ρ���-ƪ

- ���ڼ���...

��������-ƪ

- ���ڼ���...

�������� -ƪ

- ���ڼ���...

֪ʶҪ��-ƪ

- ���ڼ���...

���ʶ�̬-ƪ

- ���ڼ���...

��������-ƪ

- ���ڼ���...

ѧ��ָ��-ƪ

- ���ڼ���...

ѧ��վ��-ƪ

- ���ڼ���...